快訊

- 中國春運創單日新高!年初四人員流動量近3.53億人次

- 膜拜「克萊博國王」!挪威男子越野滑雪好手奪第6金 破冬奧單屆紀錄

- 曾出童書幫兒子克服喪父之痛 美國婦人被控正是殺夫兇手

- 初六收假日19處「魔王路段」 西部北上中午前要出發

- 光電板廠志超重訊!董座徐正民逝世 享壽72歲

- 社群瘋傳「老高與小茉」在機場遭扣留 吞18.9億天價罰單

- 五楊高架驚天跳下 35歲小黃乘客暴怒令停車!翻圍籬墜地

- 安德魯王子被捕!英國王位繼承順位考慮將他移除

- 港府提宏福苑收購方案、經費估68億港幣 7大樓「不會重建」

- 南韓「旅遊業大戶」不再是中國人? 台灣遊客成長速度居冠、韓網喊歡迎

- 當年是他提名的!最高院2大法官支持判決 川普大罵「羞恥」

- 起底醫美負責人「慘遭黑道吞千萬」 開工中4槍!倒地濺血第一現場曝光

- 機場湧人潮 空軍出動4架次C-130運輸機疏運金門旅客

- WBC》孫易磊飆速155公里!台灣隊6投手賞9K 與培證英雄握手言和

- 關稅違憲免驚 王定宇指台灣提前佈局「台積電早已領先卡位」

- 重製遊戲大師成絕響!Sony宣布3月關閉Bluepoint工作室 70名員工恐遭裁

- 美最高法院判川普關稅違法 共和黨憂恐衝擊期中選舉

- 曾推出「水晶肥皂」家喻戶曉! 南僑會長陳飛龍日前辭世 享耆壽90歲

- 扯!愛車烏來拋錨拖吊新店「不到10公里」 被開價10萬元

- 美最高院川普關稅判決震撼全球 日官員:美日合作不受影響

【決戰矽光子2-1】藉「光速」挑戰電子物理極限!一文看懂矽光子為何爆紅

2024-06-30 07:35 / 作者 戴嘉芬

護國神山台積電因應客戶需求,也投入矽光子研發。目前研發大本營位於新竹寶山鄉。路透社資料照

在 AI、HPC 等應用推動下,雲端資料中心承擔爆炸性傳輸量,傳統纜線的電子訊號傳輸已不敷使用。與傳統的電子訊號相較,光訊號具備高頻寬、低功耗、傳輸距離更遠等特點。而「矽光子」技術將光學元件用矽製程整合成晶片,把訊號由電轉為光,傳輸介質由銅導線轉為光波導,解決訊號衰減、散熱等問題,成為資料中心下一個解方。矽光子(Silicon Photonics)是透過CMOS(互補式金屬氧化物半導體)的技術,在矽晶片上整合了光電的通訊模組,以光訊號來做傳輸,以電訊號來做運算,是一種使用矽製程半導體技術所製造的光學晶片。

工研院產科國際所分析師張筠苡指出,這種技術涉及多種的光電訊號轉換,同時還需要微縮到積體電路以下的維度,因此具有相當高的技術門檻。

另一位分析師劉美君也指出,由於電子的物理極限,半導體微縮過程中會產生發熱延遲,讓傳輸速度變慢,所以需要利用光訊號來傳輸,光的能量一旦夠強,光波會變成粒子,稱為光子。光子的大小比電子小很多,而且傳輸時以「光速」在傳,能解決發熱問題。如今電子結構已無法解決散熱問題,但光子發熱問題少,相對比較不耗電,這是矽光子另一大優勢。

共同光學封裝(CPO;Co-Packaged Optics)是目前矽光子能做到的技術進展。CPO透過先進封裝技術將光子積體電路(PIC)與電子積體電路(EIC)整合在同一個基板上,來提升互連頻寬與傳輸效率。優點是減少光引擎與ASIC之間的連接距離,同時解決訊號損失的問題,因此,CPO可以說是實現矽光子在光電互連的一個重要階段。

工研院產科國際所分析師張筠苡指出,共同封裝光學CPO市場規模預計在2028年達到4050萬美元。戴嘉芬攝

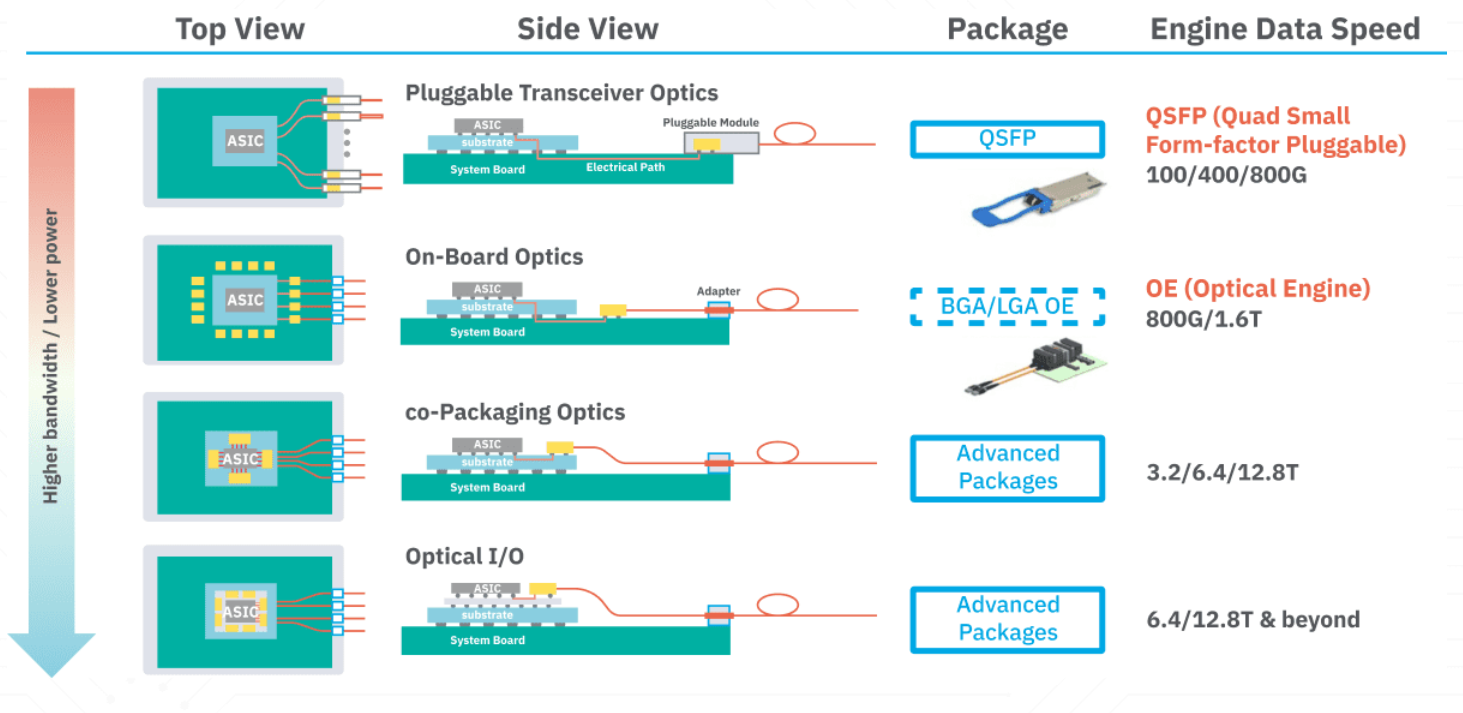

張筠苡指出,從2000年至今,市場仍以可插拔(Pluggable)光學元件為主,並朝OBO(On-Board Optics)、NPO(Near-Package Optics)型態發展,NPO、OBO都是邁向CPO之前的過渡型態。這期間,業者朝縮短光學模組跟ASIC晶片之間的距離作為研發方向,像是NPO就是在中間多放一層高性能PCB(印刷電路板),對ASIC和光學模組進行更高效整合,以提升傳輸速率,並保有訊號完整性。

CPO共同封裝光學技術架構的演變。翻攝日月光官網

國內投入矽光子研發以晶圓代工龍頭台積電和封測龍頭日月光為主。其中,日月光在此領域已耕耘十多年,日月光投控營運長吳田玉表示,矽光子技術必須長期耕耘,台灣在全球半導體產業已大贏,若繼續掌握矽光子技術,台灣半導體產業可謂如虎添翼,絕對不能放掉矽光子技術,日月光會持續研發和投資。

日月光投控營運長吳田玉本週在股東會後表示,台灣半導體產業絕對不能放掉矽光子技術。日月光提供

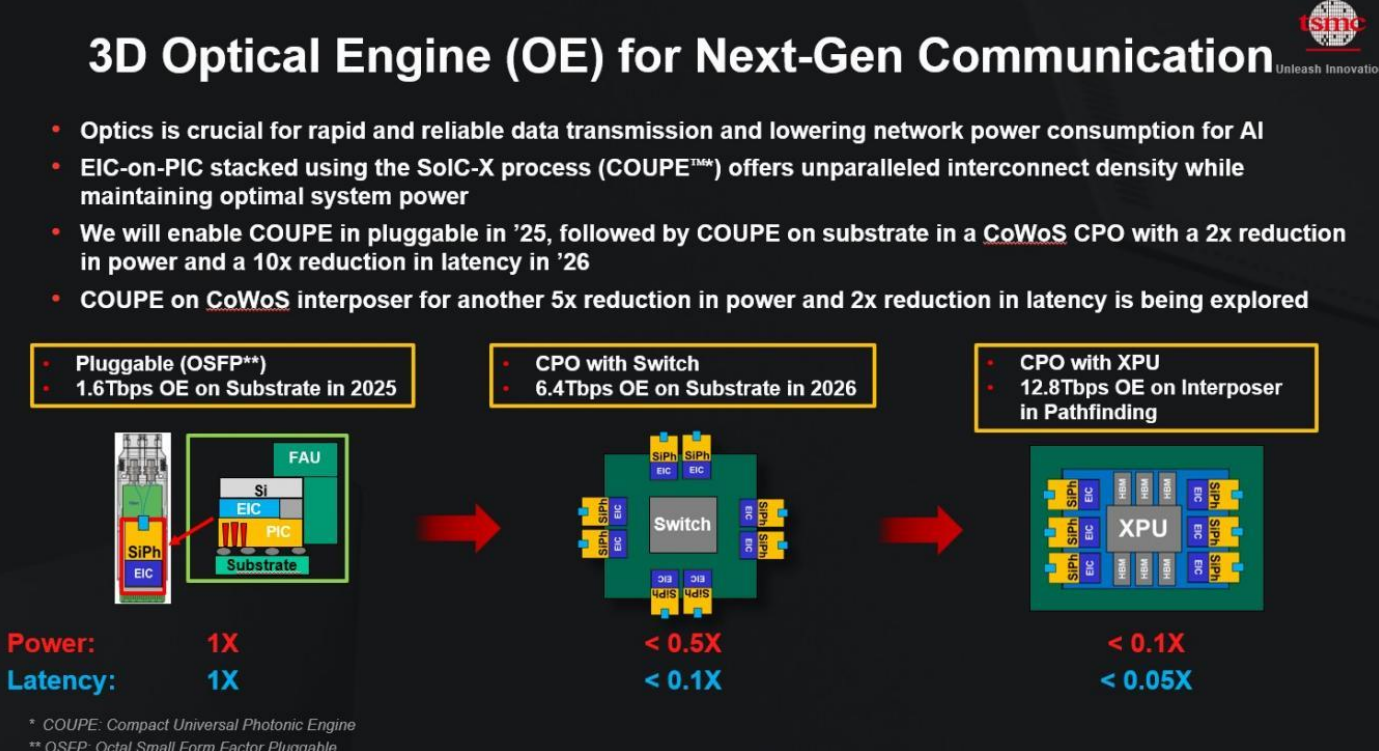

至於台積電在矽光子領域研發以「COUPE;緊湊型通用光子引擎」技術為主,COUPE使用SoIC-X晶片堆疊技術將電子裸晶堆疊在光子裸晶之上,相較於傳統的堆疊方式,能夠為裸晶對裸晶介面提供最低的電阻及更高的能源效率,能支援AI熱潮帶來的數據傳輸爆炸性成長。

在研發進程上,台積電預計於2025年完成支援小型插拔式連接器的COUPE驗證,接著於2026年將其整合於共同封裝光學元件的CoWoS封裝基板,將光連結直接導入封裝中。藉此可降低2X功耗、將延遲降低10X。

台積電還在探索一種更為先進的共同封裝光學元件方案,將COUPE整合於CoWoS中介層,進而將功耗再降低5X、將延遲再降低2X。台積電表示,矽光子是共同封裝光學元件的最佳選擇,因為其與半導體相容,且可與EIC/PIC/交換器在封裝層高度整合。

台積電正在開發用於下一代通訊的3D光學引擎技術,目標是將COUPE整合於CoWoS中介層,進一步降低功耗和延遲。取自TSMC

最新more>

熱門more>

- 社群瘋傳「老高與小茉」在機場遭扣留 吞18.9億天價罰單

- 6萬人瘋抓寶!奇美博物館上演首創「超級之夜」 造型皮卡丘、異色蒂安希都來了

- 南韓青年變「極右怪物」?厭女、仇中、政治迷因玩上癮 真相是…

- 五楊高架驚天跳下 35歲小黃乘客暴怒令停車!翻圍籬墜地

- 「森林鬼魅」寶寶露臉 蹦跳高手從6樓高躍下也沒事

- 把王淨「套牢」?曹佑寧曬戒指圖引熱議 經紀人都說了

- 美法院打臉川普關稅!南韓更焦慮? 投資綁死、退款困難、恐接更高稅率…

- 北投泡溫泉兼吃美食 北投市場黑金滷肉飯、放山雞料理獲推薦

- 中客遊貝加爾湖「墜入冰縫」7死1逃生 目擊者驚:2分鐘就消失

- 9歲童溺斃鯉魚潭!業者涉過失致死5萬元交保 檢追查有無快艇「惡意造浪」