快訊

- 快訊/美國最高法院判決川普關稅違法 「法律未授權總統徵收關稅」

- 日外相國會演說再提「竹島主權」 南韓召見公使抗議

- 美國去年第4季經濟成長放緩 全年成長為近3年最差

- 廉航德威加入 南韓所有航空禁止機上使用行動電源

- 日本最年輕冬奧金牌選手背後的男人:為她做飯、開車接送「妹妹總有一天會站上世界舞台」

- 江蕙唱一半見她衝上台突認有壓力 江淑娜搶穿戰袍討紅包

- 國道初四73起事故「回堵最長7公里」 明天北返車多!11條魔王路段曝光

- 前線照片打臉政府「沒埋地雷」說法 2柬埔寨記者遭叛國罪重判14年

- 江蕙大年初四重返小巨蛋 豪撒300個紅包

- 駐韓美軍黃海上空訓練、中國出動戰機 雙方一度對峙

- 訴訟纏身壓力大?英國快時尚ASOS創辦人泰國巴達雅墜樓亡

- 【更新】黃國昌二林拜票被嗆「臭俗辣」 嗆聲者遭志工拿糖塞嘴、候選人道歉

- 紫南宮前逃漏稅?手搖飲店公告「春節15天停開發票」挨罵 總部道歉

- 天乾物燥 日本下關寺廟失火、一家5口俱亡

- 33年來首見!美自台進口金額超越中國 汪浩:AI浪潮的歷史拐點

- 有片/泰國警察也略懂!以舞獅為掩護逮捕慣竊

- 國際金價似站穩5000美元 分析看好年底衝上6500

- 日相高市第二任施政演說提中國「脅迫」 宣布新設國家情報委員會

- 遭判無期徒刑 尹錫悅道歉但堅稱戒嚴是為了「拯救國家」

- 「BTS」V私聊閔熙珍被當呈堂證供 強調沒選邊:感到錯愕

未來電晶體架構如何發展? 台積電2奈米進度、A16、CoWos、系統級晶圓9大技術整理包

2024-05-26 12:16 / 作者 戴嘉芬

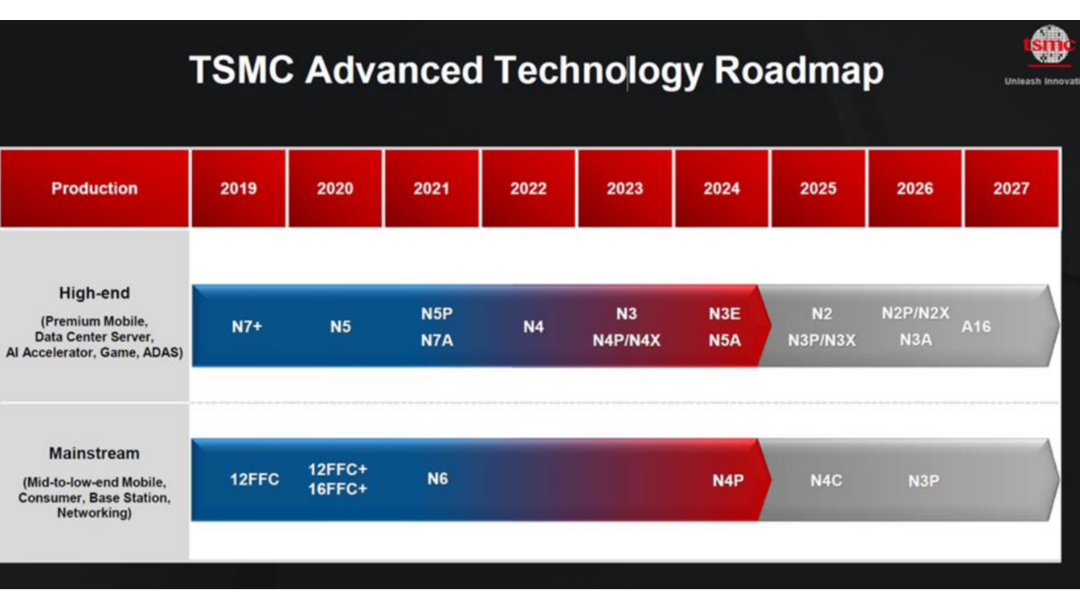

台積電今年在技術論壇發表最新製程技術藍圖,備受矚目的A16製程預計2026年下半年量產。取自TSMC

護國神山台積電周四(5/23)在新竹舉辦年度技術論壇。會中揭露3奈米、2奈米進度,以及象徵埃米(Angstrom)時代來臨的最新平台「A16」進程;還有電晶體架構在未來將會如何演變。同時也分享3DFabric先進封裝技術平台的最新發展。此外,矽光子、共同封裝光學元件等特殊製程技術,以及系統級晶圓、新的互連技術也是焦點之一。太報記者整理此次論壇9大技術重點,提供讀者參考。台積電亞洲業務處長萬睿洋在論壇中提到,2022年底,OpenAI ChatGPT橫空出世,掀起AI新浪潮!大家共同見證AI新時代到來,這是AI蓬勃發展的新篇章。根據美國富比士雜誌預測,到了2030年,在真實世界中將有超過10萬個生成式AI人形機器人。另根據研調預測,生成式AI手機全球出貨量在今年底有望達到2.4億支,將為生成式AI帶來全新體驗。

萬睿洋說,第三次工業革命由半導體技術催生,為人類帶來電腦與自動化,AI則掀起第四次工業革命!為了滿足AI創新對高效能運算的需求,3D晶片堆疊、先進封裝技術日趨重要,未來幾年實現單晶片上整合超過2000億個電晶體,並透過3D封裝達到超過1兆個電晶體,這是振奮人心的半導體技術突破。

台積電業務開發、海外營運資深副總暨副共同營運長張曉強則表示,現在不論走到哪裡,聽到的都是AI,而AI的背後則由先進半導體技術主導,若沒有先進半導體技術,無法支撐AI如此龐大的運算需求。台積電持續投資先進技術,研發預算不斷增長,以因應技術發展的需求。而對於客戶來說,技術藍圖的可預測性是非常重要的。他們的產品與技術的結合,取決於未來發展,以及台積電能否提供技術的能力。

台積電業務開發、海外營運資深副總暨副共同營運長張曉強於新竹技術論壇分享技術領先重點。取自TSMC

台積電重要技術發展內容如下:

張曉強提到,N3E(第二代3奈米)已依計畫於2023年第四季進入量產,客戶產品有出色良率,能充分支持他們產品上市計畫。此外,台積電也成功開發出N3P技術,該技術已通過驗證,其良率表現接近於N3E。N3P 已經收到了客戶產品設計定案(product tape-outs),將於2024年下半年開始量產。

他強調,由於N3P在效能、功耗、面積(PPA)方面表現更為優異,效能提升45%,密度改善4%。因此未來大多數3奈米產品都將採用N3P製程,台積電還有針對高性能運算推出的N3X,估計之後會有更多手機、HPC應用採用3奈米製程。

張曉強說,N2(2奈米)技術是一個革命性的節點,將電晶體架構從FinFET(鰭式場效電晶體)改為Nanosheet(奈米片電晶體),透過持續強化且具創新結構的設計技術協同優化,奈米片電晶體提供優異的能源效率;目前進展順利,轉換目標達90%,換成良率則超過80%,N2目標是在2025年下半年進入量產。

針對製程後段,台積電導入了新的製程與材料,將電阻/電容延遲(RC delay)降低高達10%,並提供友好設計規則,能夠增加3%~4%的邏輯密度。此外,為了強化功率傳輸,台積電還提供了超高性能金屬/絕緣體/金屬電容(SHPMIM),其容量密度是上一代技術的兩倍之多。

其次,透過元件寬度調節,N2搭配NanoFlex創新技術可將PPA的優勢發揮到最大化。使高度較低的元件能夠有效節省面積,並擁有更高的能源效率,而高度較高的元件則將效能最大化。客戶可在相同的設計區塊中優化高低元件組合,提升15%的速度,同時在面積與能源效率間取得最佳平衡。

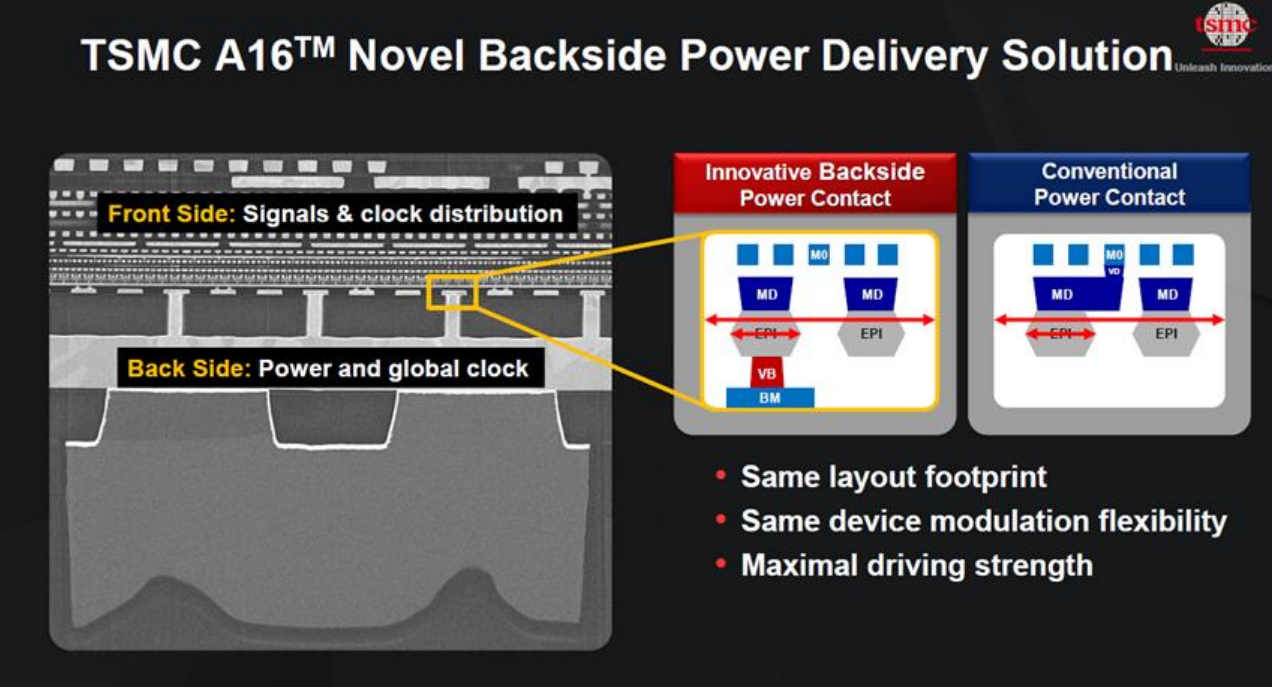

張曉強表示,今年甫發表的A16是台積電最重要的技術平台,將晶片的PPA(效能、功耗、面積)發揮到極致。它象徵我們已經結束奈米(Nanometer)時代,現在將進入埃米(Angstrom)時代。因此,台積電正在把N命名慣例轉變為A,A16計畫於2026年下半年量產。

在換算上,1埃米等於0.1奈米,因此16A也相當於1.6奈米。

張曉強表示,A16是下一代奈米片電晶體(Nanosheet)技術,它多了一個創新架構,也就是超級電軌(Super Power Rail)架構,這是一種創新的最佳晶圓背面供電網路解決方案。A16將供電網路移到晶圓背面,把電晶體連接從前面移至後面,利用這種普通的連接技術與背面供電網路能力結合在一起,進而在晶圓正面釋出更多訊號網路的佈局空間,藉以提升邏輯密度和效能,而不會浪費空間。它讓效能最高提升了10%,功率最多降低了20%,晶片密度最多提高了10%,PPA有了顯著的提升。

張曉強強調,台積電開發的此種創新晶圓背面傳輸方案為業界首創,保留了柵極密度與元件寬度的彈性。A16 是具有複雜訊號佈線及密集供電網路的高效能運算(HPC)產品的最佳解決方案。

A16將供電網路移到晶圓背面,在晶圓正面釋出更多訊號網路的佈局空間。取自TSMC

相較台積電N2P製程,A16在相同Vdd (工作電壓)下,速度增快8~10%,在相同速度下,功耗降低15~20%,晶片密度提升高達1.10X。

電晶體架構從平面式(Planer)發展到FinFET(鰭式場效電晶體),並即將轉變至Nanosheet(奈米片電晶體)架構。在奈米片之後,台積電認為垂直堆疊CFET(互補式場效電晶體)是未來製程架構選項之一。

台積電積極研究將CFET用於未來製程架構的可能性。台積電預估,在考量佈線和製程複雜性後,藉由不同材料的上下堆疊,讓垂直堆疊的不同場效電晶體更為靠近,除了改善電流之外,CFET還可將密度提升1.5至2倍,強調CFET不僅是紙上談兵,目前已進入研發驗證階段。除了CFET,台積電在低維材料方面取得了突破,可能實現進一步的尺寸和能源微縮。

台積電計畫導入新的互連技術,以提升互連效能。首先針對銅互連技術,預計導入一個全新的通路結構(via scheme),進而將業界領先的通路電阻(via resistance)再降低25%。還在研發一種新的銅阻障方案(Cu barrier),可以降低約 15%的銅線電阻。

其次,計畫採用一種全新的通路蝕刻停止層(via etch-stop-layer),可降低約6%的耦合電容。

除了銅互連之外,台積電還在研發一種含有氣隙的新型金屬材料,可降低約 25%的耦合電容。此外,嵌入石墨烯(Intercalated graphene)也是一種極具前景的新材料,可大幅縮短互連延遲。

TSMC 3DFabric技術家族包含三大平台:包括適用於3D小晶片堆疊技術TSMC-SoIC、CoWoS和InFO。

台積電的系統整合晶片(SoIC)已成為3D晶片堆疊的領先解決方案,客戶越來越趨向採用CoWoS搭配SoIC及其他元件的做法,以實現最終的系統級封裝(System in Package, SiP)整合。

SoIC平台用於3D矽晶片堆疊,並提供SoIC-P和SoIC-X兩種堆疊方案。SoIC-P是一種微凸塊堆疊解決方案,適用於講求成本效益的應用,如行動式應用。

SoIC-X 則是一項無凸塊堆疊解決方案,無論是現有的9微米鍵合間距前到後堆疊方案(front-to-back scheme),還是將於2027年上市的 3 微米鍵合間距前到前堆疊方案(front-to-front scheme),其裸晶到裸晶(die-to-die)互連密度均比40微米到18微米間距的微凸塊前到前堆疊方案高出10X以上。此技術適用於對效能要求極高的各類高效能運算(HPC)應用。台積電看到客戶對於SoIC-X技術的需求逐漸增加,預計到2026年底將會有30個客戶設計定案。

還有InFO PoP和 InFO-3D適用於高階行動式應用,InFO 2.5D則適用於高效能運算的小晶片整合。客戶可根據產品需求,將SoIC晶片與CoWoS或InFO進行整合。

CoWoS平台包括目前成熟度最高、採用矽中介層的CoWoS-S,以及採用有機中介層的CoWoS-L和CoWoS-R。

台積電表示,CoWoS是AI設計的關鍵推動技術,讓客戶能夠在單一中介層上,放置更多的處理器核心及高頻寬記憶體(HBM)。CoWos可將先進的SoC或SoIC晶片與先進的高頻寬記憶體進行整合,進而滿足市面上AI晶片的嚴苛要求。

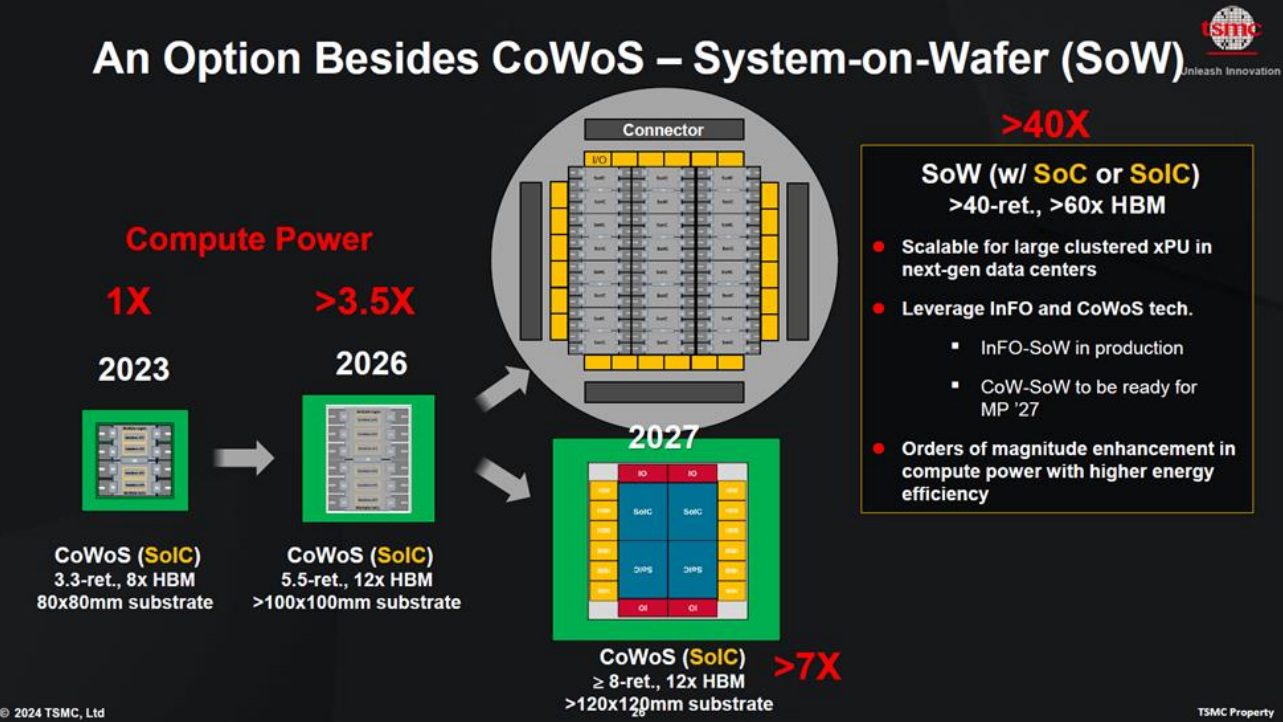

台積電表示,客戶大多希望能進一步發展CoWoS,讓CoWos和更多邏輯與記憶體整合在一起。有鑒於此,中介層的尺寸擴大了,透過光罩尺寸的數量來衡量,目前最先進的中介層技術約為光罩尺寸的 3.3 倍;之後將可達到 5.5 倍。台積電已與客戶討論將中介層拓展到做最多7至8倍的光罩尺寸。展望未來,公司正在努力將晶圓級整合引進通用平台解決方案,將更多的運算功能、更多的記憶體頻寬整合在一起,以實現AI應用。

台積電SoIC已透過CoWoS-S量產出貨,並計畫開發一種8倍光罩尺寸且具備採用A16製程技術的SoIC晶片和12個高頻寬記憶體堆疊的CoWoS解決方案, 並預計將於2027年開始量產。

直至今年年底,台積電將為超過25個客戶啟動超過150個CoWoS客戶產品設計定案。舉例,台積電與NVIDIA合作推出了Blackwell AI加速器,這是全球首款量產並將2個採用5奈米製程技術的SoC和8個高頻寬記憶體堆疊整合在一個模組中的CoWoS-L產品。

台積電正在研發InFO-oS及CoWoS-R解決方案,支援先進駕駛輔助系統(ADAS)、車輛控制及中控電腦等應用,預計於2025年第四季完成AEC-Q100第二級驗證。

台積電表示,先進封裝對於車用產品也非常重要,因為汽車製造商真的很喜歡這種小晶片解決方案。他們可以混搭不同的設計來滿足不同車款、不同市場和不同價格帶的需求。因此,台積電為汽車產業創造了兩種整合式解決方案:一種是來自手機解決方案的InFO,另一種是來自高效能運算解決方案的 CoWoS-R。透過這兩種解決方案,客戶可自行進行設計,以因應非常廣泛的應用。例如:為高階車款快速設計一個系統,可搭配不同的小晶片,就可應用在中階車款。這就是台積電為客戶提供靈活設計的例子。

張曉強表示,系統級晶圓技術(SoW)採用台積電成熟的InFO和CoWoS 技術,以擴充下一代資料中心所需的運算能力。目前採用InFO技術的系統級晶圓已經量產。

台積電首款InFO–SoW系統級晶圓產品,即是特斯拉超級電腦自製晶片Dojo,提供高速運算客製化需求,且不需要額外PCB載板,就能將相關晶片整合散熱模組,加速生產流程。

而採用CoWoS技術的系統級晶圓,能夠整合SoC或SoIC、HBM及其他元件,打造出一個強大且運算能力媲美資料中心甚至整台伺服器的晶圓級系統,預計於2027年開始量產。

採用CoWoS技術的系統級晶圓,預計於2027年開始量產。取自TSMC

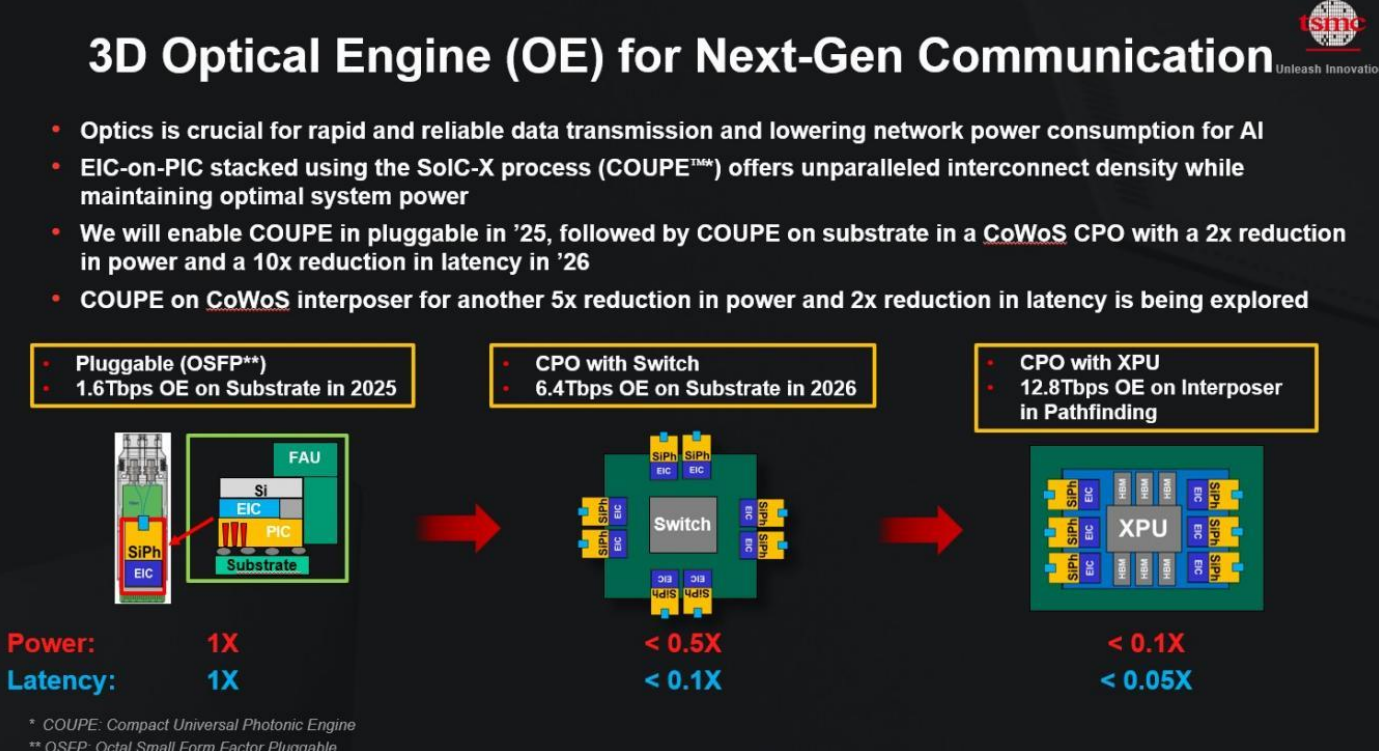

台積電正在研發緊湊型通用光子引擎(COUPE)技術,以支援AI熱潮帶來的數據傳輸爆炸性成長。COUPE使用SoIC-X晶片堆疊技術將電子裸晶堆疊在光子裸晶之上,相較於傳統的堆疊方式,能夠為裸晶對裸晶介面提供最低的電阻及更高的能源效率。

台積電正在開發用於下一代通訊的3D光學引擎技術。取自TSMC

台積電預計於2025年完成支援小型插拔式連接器的COUPE驗證,接著於2026年整合CoWoS封裝成為共同封裝光學元件(Co-Packaged Optics, CPO),將光連結直接導入封裝中。藉此可降低2X功耗、將延遲降低10X。

台積電還在探索一種更為先進的共同封裝光學元件方案,將COUPE整合於CoWoS中介層,進而將功耗再降低5X、將延遲再降低2X。

台積電表示,矽光子是共同封裝光學元件(Co-Packaged Optics, CPO)的最佳選擇,因為其與半導體相容,且可與EIC/PIC/交換器在封裝層高度整合。COUPE技術透過最短路徑的同質銅-銅介面整合電子積體電路(PIC)和光子積體電路(EIC),進而實現超高速射頻(RF)訊號(200G/λ)。台積電COUPE解決方案可最小化使用面積,且具備光柵耦合器(GC)和邊際耦合器(EC),可滿足客戶的各式需求。

最新more>

- 北投泡溫泉兼吃美食 北投市場黑金滷肉飯、放山雞料理獲推薦

- 快訊/美國最高法院判決川普關稅違法 「法律未授權總統徵收關稅」

- 日外相國會演說再提「竹島主權」 南韓召見公使抗議

- 美國去年第4季經濟成長放緩 全年成長為近3年最差

- 廉航德威加入 南韓所有航空禁止機上使用行動電源

- 日本最年輕冬奧金牌選手背後的男人:為她做飯、開車接送「妹妹總有一天會站上世界舞台」

- 插隊搶自由座!高鐵白衣男爆出是牙醫 黑歷史曝光、退追柯文哲

- 江蕙唱一半見她衝上台突認有壓力 江淑娜搶穿戰袍討紅包

- 國道初四73起事故「回堵最長7公里」 明天北返車多!11條魔王路段曝光

- 前線照片打臉政府「沒埋地雷」說法 2柬埔寨記者遭叛國罪重判14年

熱門more>

- 分析:中國對非洲全境宣布零關稅政策 但想倚重的非洲同伴是哪種國家?

- 谷愛凌在美生長卻代表中國出賽 美副總統范斯說話了

- 「今天,我為龍一滑冰!」七年羈絆逆轉勝 「璃龍組」為日本雙人花滑摘首金

- 谷愛凌為何棄美投中?美媒:中國提供數百萬美元資金

- 2026最受矚目「漫改真人版」要來了!《我獨自升級》、《驀然回首》、《海洋奇緣》期待值爆表

- 日本雙人花滑「木原運送」超吸睛!木原龍一親揭原因:不希望璃來受傷

- 「森林鬼魅」寶寶露臉 蹦跳高手從6樓高躍下也沒事

- 同為華裔冬奧明星 為何谷愛凌被罵叛徒?劉美賢頂六四光環?

- 川普關稅擋不了逆差擴大 台灣貨品貿易逆差翻倍

- 「週末都在工地搬磚」苦等12年冬奧終摘銀 他頒獎台上跪拜叩首